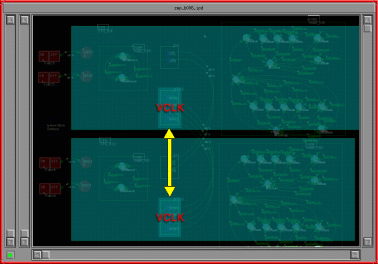

The VCLK allows the generation of a system wide virtual clock. It allows several CPUs of varying speeds to be connected to a common free running clock signal. This clock ensures that all CPUs are never more than one virtual clock cycle apart.

A CPU with a VCLK component can opt into or out of the system wide virtual clock. By opting in, it ensures that it will keep pace with the rest of the system. By opting out, it enables the rest of the system to run at maximum speed. A CPU may continually opt in and out depending on its work load and impact on the rest of the system.

All CPUs with a participating VCLK component have an associated VCLK counter plus offset. The offset is imaginary and once the VCLK starts participating in the system wide virtual clock, the offset is fixed and remains constant. If the whole system is stopped at any time the difference between any two participating vclk counters (plus associated offsets) will never be greater than one.

The VCLK is driven by the state machine schedular as a background task.

When using the VCLK to synchronise message broadcasting, the software should wait for at least two VCLK cycles (the VCLK counter should change by two). This will guarentee that all other participating CPUs have seen the message.

The VCLK component generates machine code which is directly executable in the target system. No additional debug code is generated for the target when the simulator is used in place of a real CPU. Signaling between different CPUs is performed by reading from and writing to real CPU I/O ports. The simulator uses I/O components mapped to the CPU's I/O ports to route the signals between simulated CPUs. (see I/O components above for further information).